楷登電子(美國Cadence公司)近日發佈已經過數百次先進工藝節點成功流片驗證的新版CadenceÒ數字全流程,進一步優化功耗,性能和麵積,廣泛應用於汽車,移動,網路,高性能計算和人工智慧(AI)等各個領域。流程採用了支持機器學習(ML)功能的統一佈局佈線和物理優化引擎等多項業界首創技術,吞吐量最高提升3倍,PPA最高提升20%,助力實現卓越設計。

買IC網 - 電子元器件代理與採購 | IC交易網 - 買IC就找買IC網

經過多項關鍵技術,全新Cadence數字全流程實現了PPA和吞吐量的進一步提升:

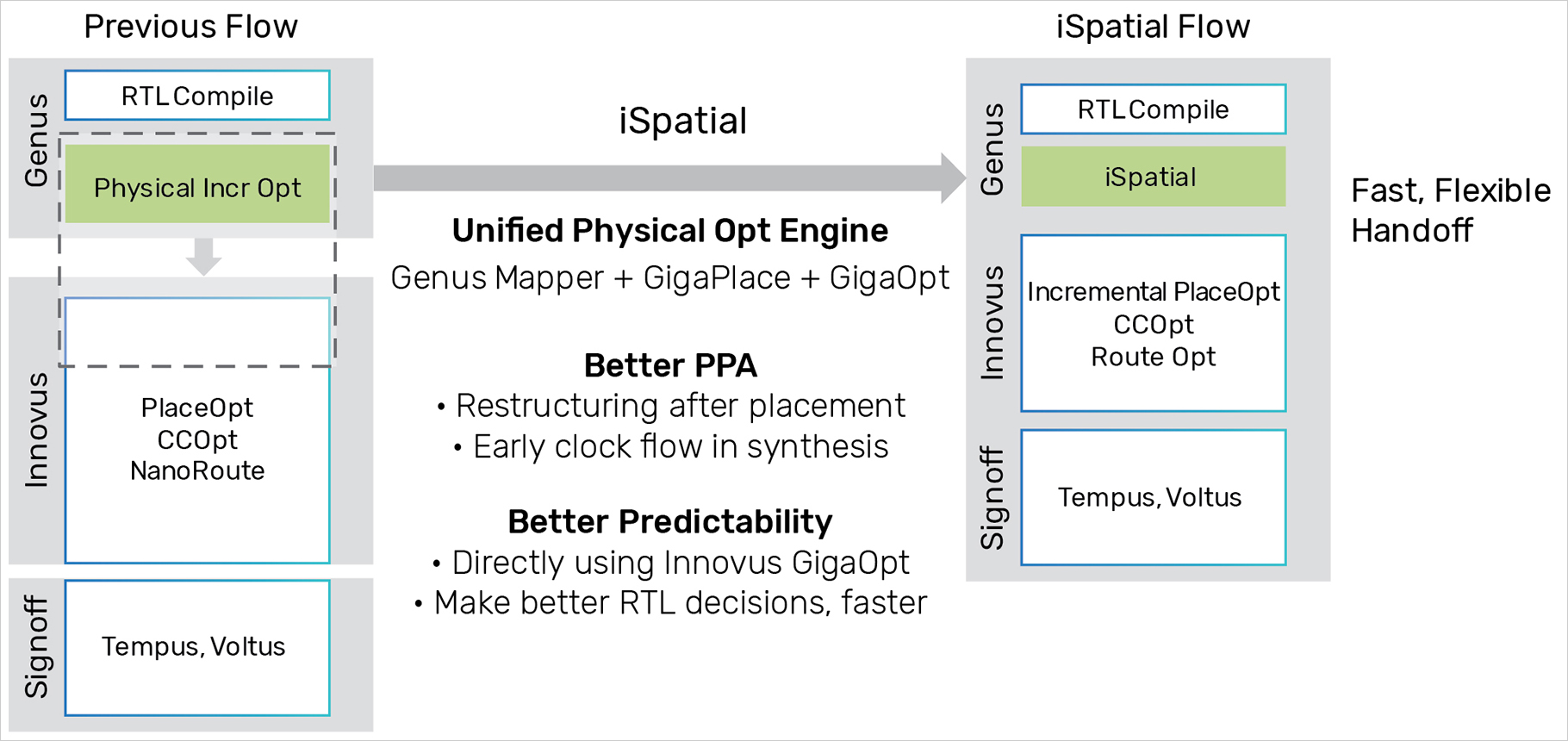

· Cadence數字全流程iSpatial技術:iSpatial技術將Innovus設計實現系統的GigaPlace佈線引擎和GigaOpt優化器集成到Genus綜合解決方案,支持佈線層分配,有效時鐘偏移和通孔支柱等特性。iSpatial技術讓用戶可以使Luminus用統一的用戶介面和數據庫完成從Genus物理綜合到Innovus設計實現的無縫銜接。

· 機器學習(ML)功能:ML功能可以讓用戶用現有設計訓練iSpatial優化技術,實現傳統佈局佈線流程設計裕度的最小化。

· 優化簽核收斂:數字全流程採用統一的設計實現,時序簽核及電壓降簽核引擎,通過所有物理,時序和可靠性目標設計的同時收斂來增強簽核性能,幫助客戶降低設計裕度,減少迭代。

“基於已經廣泛採納的集成流程,全新的增強版數字全流程進一步強化了Cadence在數字與簽核設計領域的領導力,助力客戶實現SoC卓越設計,”Cadence公司資深副總裁兼數字與簽核事業部總經理Chin-ChiTeng博士表示。“我們與客戶緊密合作,緩解大規模設計下日益緊張的時間壓力,提供高效達成PPA目標的全部所需。”

Cadence數字全流程包括Innovus設計實現系統,Genus綜合解決方案,Tempus時序簽核解決方案和Voltus IC電源完整性解決方案。流程為客戶提供實現設計收斂的快速路徑和更好的可預測性,支持公司的智能系統設計戰略,助力實現高級節點片上系統(SoC)的卓越設計。

客戶回饋

“我們一直不遺餘力地讓高性能核心滿足越來越高的性能目標。通過Innovus設計實現系統GigaOpt優化器工具新增的ML能力,我們得以快速完成CPU核心的自動訓練,提高最大頻率,並將時序總負餘量降低80%。簽核設計收斂的總周轉時間可以縮短2倍。"——MediaTek公司計算和人工智慧技術事業部總經理,Dr.SAHwang

MediaTek公司計算和人工智慧技術事業部總經理,Dr.SAHwang

“Cadence數字全流程的iSpatial技術可以精確預測完整佈局對PPA的優化幅度,實現RTL,設計約束和佈局佈線的快速迭代,總功耗減少6%,且設計周轉時間加快3倍。同時,Cadence獨特的ML能力讓我們在Samsung Foundry的4nmEUV節點訓練設計模型,實現了5%額外性能提升和5%漏電功率減少。”——Samsung Electronics代工設計平臺開發執行副總裁,JaehongPark